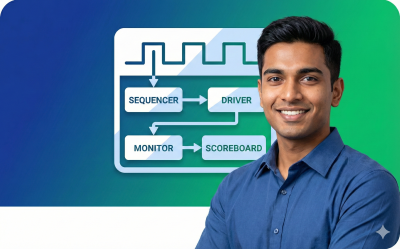

System Verilog for Design & Verification

Learn SystemVerilog from fundamentals to advanced verification concepts including testbench development, interfaces, assertions, and functional coverage for modern VLSI workflows.

English

Last updated

Wed, 18-Feb-2026